#### DPG3

The DPG3, or Data Pattern Generator 3, is a device designed to support the evaluation of Analog Devices' High-Speed Digital-to-Analog Converters (DAC). The device is connected to a PC over USB, and allows a user to download a data vector into the DPG3, which is then played out to an attached DAC evaluation board at full speed.

**Please note:** Analog Devices' pattern generators and high-speed DAC evaluation boards are designed and sold solely to support an efficient and thorough means by which to evaluate Analog Devices high speed DACs in a lab environment for a wide range of end applications. Any application or use of the pattern generators and/or high-speed DAC evaluation boards, other than specified above, will not be supported.

This page describes the hardware of DPG3. The device can be driven from many different software applications. For more information on the software, please see the High-Speed DAC Software Suite documentation.

For information on the DPG2, the predecessor to the DPG3, please see the DPG2 page.

## **Ordering Code**

The part number for the DPG3 is AD-DPG3.

# **Hardware Specifications**

Please note that not all hardware options and specifications are supported with any particular evaluation board or software package. Specifications are subject to change without notice.

#### Converter Interfaces

- CMOS Interface

- 32-bits (shared with the P lines of the LVDS bus)

- Up to 250Mbps per bit(SDR)

- Same connector and pinout as DPG2

- LVDS Interface

- 32-bits (P lines shared with CMOS interface)

- Up to 1.6Gbps per bit (800MHz DDR)

- Same connector and pinout as DPG2

- High-Speed Serial Interface (For JESD204 Converters)

- 16 Tx lanes

- Up to 8.5Gbps per lane

- Memory

- Dual DDR3 SO-DIMM

- Maximum pattern length of 134M samples (limited to 30M samples in most 3'rd party software)

- PC Interface

- ∘ USB 2.0 "B" connector

- Clocking

- On-connector clock input for all interfaces

- Optional external clock input via front-panel SMA jack for CMOS and LVDS interfaces

- Trigger

- SMA jack for trigger input or output

- Multi-Unit Synchronization

- Up to four DPG3's may have their LVDS interfaces synchronized together

- Requires additional Synchronization Board and cabling

- Specified for operation at 25°C only

Some PCs with USB 3.0 *SuperSpeed* ports have been unable to communicate reliably with the DPG3. On these PCs, the standard USB 2.0 ports (without the DPG3.

## **Output Data**

The vector length must be at least 64 points per channel, and the vector length must be divisible by 64 for proper operation.

# **Clocking**

The clocking system varies between the traditional CMOS/LVDS interfaces and the newer high-speed serial interface. In all cases, the DPG needs to be provided with a clock. It cannot generate a data clock internally.

#### **CMOS/LVDS**

Most evaluation boards will supply a clock to the DPG over the CMOS/LVDS connector. In all cases, this clock is LVDS, even if the rest of the interface is CMOS. A clock will be provided with the data that is synchronous to the data (source synchronous), which will match the format of the data.

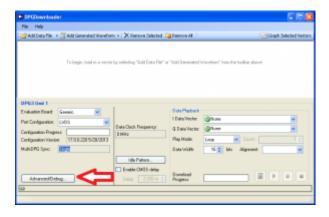

Alternatively, a clock can be provided externally via the SMA jack on the front of the unit. In this case, the clock's amplitude must be +4dBm. This method is not recommended for general use. To enable the external clock operation, click the *Advanced/Debug* button in DPGDownloader, and select *Front panel SMA jack* as the Clock Source in the Clock section.

#### **High-Speed Serial**

The high-speed serial transceivers inside the DPG3 require a reference clock in order to be able to lock on to the embedded clock inside the serial data stream. This clock must be provided over the connector to the evaluation board.

## **External Trigger**

The SMA jack on the front of the unit for the trigger can be used either as an input or as an output trigger. To enable the trigger, click *Advanced/Debug* in DPGDownloader, and check the *Enable Trigger* box in the Trigger section.

#### **Input Trigger**

When set as an input, the unit will start playback when the trigger is asserted (raised from low to high).

The input high threshold is 2.0V, and the input low threshold is 0.8V, allowing it to be directly interfaced with 3.3V logic signals.

#### **Output Trigger**

When set as an output, the trigger will pulse when the playback is running at the beginning of the vector. Therefore, it will pulse every time the vector is looped when in Loop mode, or only once if the unit is in Count mode.

## **Multi-Unit Synchronization**

With the appropriate external synchronization board and cables, up to four DPG3's can be synchronized together when in LVDS mode. One unit is designated as the master, and all units use the master's clock instead of their own. The data will then being playback from each unit on the same clock edge.

Synchronizing multiple DPGs together does *not* guarantee that the analog waveforms coming out of the attached DAC evaluation board are synchronized. Each particular DAC may require additional synchronization circuitry to ensure that the analog outputs are synchronized.

Note that the synchronization board and cables used with the DPG2 are not compatible with the DPG3

Multi-Unit Synchronization is not currently supported on the DPG3, but will be enabled by a future software update.

### **Connector Pinouts**

The DGP3 has two separate connector systems for interfacing with evaluation boards. One, for CMOS and LVDS interface DACs, is backwards compatible with the DPG2. The second connector is new to the DPG3, and supports high-speed serial, power, and communications.

#### **CMOS/LVDS Pinout**

The CMOS/LVDS connection on DPG2 and DPG3 uses two AMP/Tyco 1469169-1 connectors, placed side-by-side, with 139.2mil spacing between the centers of the innermost pins on both connectors. The mating connector on the evaluation board side is two AMP/Tyco 1469028-1. Note that both connectors are always required.

#### **Left Side Connector**

The left connector when looking at the connection on the DPG from the evaluation board side (J17 on the DPG2, J8 on the DPG3)

| A1 CLK_DCOA_P  B1 CLK_DCOA_N  B1 CLK_DCOA_N  B2 CLK_TXI_O_P  B2 CLK_TXI_O_P  B3 CLK_TXI_O_P  B4 CLK_TXI_O_P  B5 CLK_TXI_O_N  B5 CLK_TXI_O_N  B6 CLK_TXI_O_N  B6 CLK_TXI_O_N  B7 CHANNEL  B7 CHANNEL  B8 CLK_TXI_O_N  B8 CLK_TXI_O_N  B8 CLK_TXI_O_N  B9 CLK_TX | Pin  | Name         | Description                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|---------------------------------------------------------------------------------------------|

| A2 CLK_TXI_O_P  A3 CLK_TXI_O_P  B52 CLK_TXI_O_N  B64 Clock output from DPG, synchronous with "I" data. Positive side of differential signal.  A3 TXI_DATA_P15  "I" channel data bit 15.  B3 TX_DATA_N15  "I" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode.  A4 TXI_DATA_N14  "I" channel data bit 14, negative side in LVDS mode. Not used in CMOS mode.  A5 TXI_DATA_N14  "I" channel data bit 11, negative side in LVDS mode. Not used in CMOS mode.  A6 TXI_DATA_P13  "I" channel data bit 13, negative side in LVDS mode. Not used in CMOS mode.  A7 TXI_DATA_P13  "I" channel data bit 12, negative side in LVDS mode. Not used in CMOS mode.  A7 TXI_DATA_P13  "I" channel data bit 12, negative side in LVDS mode. Not used in CMOS mode.  A7 TXI_DATA_P11  "I" channel data bit 11, negative side in LVDS mode. Not used in CMOS mode.  A8 TXI_DATA_P11  "I" channel data bit 11, negative side in LVDS mode. Not used in CMOS mode.  A8 TXI_DATA_P11  "I" channel data bit 10, negative side in LVDS mode. Not used in CMOS mode.  A8 TXI_DATA_P10  "I" channel data bit 10, negative side in LVDS mode. Not used in CMOS mode.  A8 TXI_DATA_P10  "I" channel data bit 19.  B9 TXI_DATA_P9  "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode.  A10 TXI_DATA_P9  "I" channel data bit 8.  B10 TXI_DATA_N8  "I" channel data bit 9.  B10 TXI_DATA_N8  "I" channel data bit 9.  B10 TXI_DATA_N8  "I" channel da | A1   | CLK_DCOA_P   |                                                                                             |

| AZ CLK_TXI_O_N differential signal.  B2 CLK_TXI_O_N differential signal.  A3 TXI_DATA_P15 "I" channel data bit 15.  B3 TXI_DATA_P15 "I" channel data bit 15.  B3 TXI_DATA_P14 "I" channel data bit 15.  B3 TXI_DATA_P14 "I" channel data bit 14.  A4 TXI_DATA_P15 "I" channel data bit 14.  A5 TXI_DATA_P13 "I" channel data bit 14.  A6 TXI_DATA_P13 "I" channel data bit 13.  B5 TXI_DATA_P13 "I" channel data bit 13.  B5 TXI_DATA_P13 "I" channel data bit 13.  B6 TXI_DATA_P13 "I" channel data bit 13.  B6 TXI_DATA_P13 "I" channel data bit 12.  B6 TXI_DATA_P12 "I" channel data bit 12.  B7 TXI_DATA_P11 "I" channel data bit 11.  B7 TXI_DATA_P11 "I" channel data bit 11.  B7 TXI_DATA_P11 "I" channel data bit 11.  B8 TXI_DATA_P11 "I" channel data bit 11.  B8 TXI_DATA_P11 "I" channel data bit 11.  B8 TXI_DATA_P10 "I" channel data bit 10.  B9 TXI_DATA_P10 "I" channel data bit 19.  B9 TXI_DATA_P10 "I" channel data bit 19.  B1 TXI_DATA_P10 "I" channel data bit 19.  B1 TXI_DATA_P10 "I" channel data bit 19.  B2 TXI_DATA_P10 "I" channel data bit 18.  B10 TXI_DATA_P10 "I" channel data bit 8.  B10 TXI_DATA_N8 "I | В1   | CLK_DCOA_N   | Data Clock Out from the DUT, into the DPG. Negative side of differential signal. (required) |

| SZ   CLK_IT_U_N   differential signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A2   | CLK_TXI_O_P  |                                                                                             |

| TXI_DATA_N15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | B2   | CLK_TXI_O_N  | · · · · · · · · · · · · · · · · · · ·                                                       |

| A4 TXI_DATA_P14 "I" channel data bit 14.  B4 TXI_DATA_N14 "I" channel data bit 14, negative side in LVDS mode. Not used in CMOS mode. A5 TXI_DATA_N13 "I" channel data bit 13, negative side in LVDS mode. Not used in CMOS mode. A6 TXI_DATA_N13 "I" channel data bit 13, negative side in LVDS mode. Not used in CMOS mode. A6 TXI_DATA_N12 "I" channel data bit 12, negative side in LVDS mode. Not used in CMOS mode. A7 TXI_DATA_N12 "I" channel data bit 11, negative side in LVDS mode. Not used in CMOS mode. A7 TXI_DATA_P11 "I" channel data bit 11.  B7 TXI_DATA_P11 "I" channel data bit 11, negative side in LVDS mode. Not used in CMOS mode. A8 TXI_DATA_N10 "I" channel data bit 10.  B8 TXI_DATA_N10 "I" channel data bit 10.  B8 TXI_DATA_N10 "I" channel data bit 9.  B9 TXI_DATA_N19 "I" channel data bit 9.  B9 TXI_DATA_N19 "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode. A10 TXI_DATA_N8 "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode. A10 TXI_DATA_N8 "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode. Digital Ground Digital Gro | A3   | TXI_DATA_P15 | "I" channel data bit 15.                                                                    |

| B4       TXI_DATA_N14       "I" channel data bit 14, negative side in LVDS mode. Not used in CMOS mode.         A5       TXI_DATA_P13       "I" channel data bit 13.         B5       TXI_DATA_P12       "I" channel data bit 13, negative side in LVDS mode. Not used in CMOS mode.         A6       TXI_DATA_P12       "I" channel data bit 12, negative side in LVDS mode. Not used in CMOS mode.         A7       TXI_DATA_P11       "I" channel data bit 11.         B7       TXI_DATA_P11       "I" channel data bit 11.         B7       TXI_DATA_P10       "I" channel data bit 11.         B8       TXI_DATA_N10       "I" channel data bit 10.         B8       TXI_DATA_P10       "I" channel data bit 10, negative side in LVDS mode. Not used in CMOS mode.         A9       TXI_DATA_P9       "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode.         A10       TXI_DATA_P9       "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode.         B10       TXI_DATA_P8       "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode.         B21       GROUND       Digital Ground         B32       GROUND       Digital Ground         B43       GROUND       Digital Ground         B44       GROUND       Digital Ground         B55       GROUND       D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | В3   | TXI_DATA_N15 | "I" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode.                 |

| A5 TXI_DATA_P13 "I" channel data bit 13. B5 TXI_DATA_N13 "I" channel data bit 13, negative side in LVDS mode. Not used in CMOS mode. A6 TXI_DATA_N12 "I" channel data bit 12, negative side in LVDS mode. Not used in CMOS mode. A7 TXI_DATA_N11 "I" channel data bit 11. B8 TXI_DATA_N11 "I" channel data bit 11. B7 TXI_DATA_N11 "I" channel data bit 11. B8 TXI_DATA_N11 "I" channel data bit 10. B8 TXI_DATA_N10 "I" channel data bit 10. B8 TXI_DATA_P10 "I" channel data bit 10. B8 TXI_DATA_P9 "I" channel data bit 10. B9 TXI_DATA_P9 "I" channel data bit 9. B9 TXI_DATA_N9 "I" channel data bit 9. B1 TXI_DATA_N9 "I" channel data bit 9. B1 TXI_DATA_N9 "I" channel data bit 9. B2 TXI_DATA_N9 "I" channel data bit 8. B10 TXI_DATA_N8 "I" channel data bit 8. B10 TXI_DATA_N9 Digital Ground B64 GROUND Digital Ground B65 GROUND Digital Ground B66 GROUND Digital Ground B67 GROUND Digital Ground B68 GROUND Digital Ground B69 GROUND Digital Ground B60 GROUND Digital Ground B61 GROUND Digital Ground B62 GROUND Digital Ground B63 GROUND Digital Ground B64 GROUND Digital Ground B65 GROUND Digital Ground B66 GROUND Digital Ground B67 GROUND Digital Ground B68 GROUND Digital Ground B69 GROUND Digital Ground B60 GROUND Digital Ground B61 GROUND Digital Ground B62 GROUND Digital Ground B63 GROUND Digital Ground B64 GROUND Digital Ground B65 GROUND Digital Ground B66 GROUND Digital Ground B67 GROUND Digital Ground B68 GROUND Digital Ground B69 GROUND Digital Ground B60 GROUND Digital Ground B61 GROUND Digital Ground B62 GROUND Digital Ground B63 GROUND Digital Ground B64 GROUND Digital Ground B65 GROUND Digital Ground B66 GROUND Digital Ground B67 GROUND Digital Ground B68 GROUND Digital Ground B69 GROUND Digital Ground B60 GROUND Digital Ground B61 GROUND Digital Ground B62 GROUND Digital Ground B63 GROUND Digital Ground B64 GROUND Digital Ground B65 GROUND Digital Ground B66 GROUND Digital Ground GROUND Digital Ground GROUND Di | A4   | TXI_DATA_P14 | "I" channel data bit 14.                                                                    |

| B5       TXI_DATA_N13       "I" channel data bit 13, negative side in LVDS mode. Not used in CMOS mode.         A6       TXI_DATA_P12       "I" channel data bit 12.         B6       TXI_DATA_N12       "I" channel data bit 12, negative side in LVDS mode. Not used in CMOS mode.         A7       TXI_DATA_P11       "I" channel data bit 11, negative side in LVDS mode. Not used in CMOS mode.         A8       TXI_DATA_N10       "I" channel data bit 10.         B8       TXI_DATA_N10       "I" channel data bit 10.         B8       TXI_DATA_N10       "I" channel data bit 10.         B9       TXI_DATA_N90       "I" channel data bit 9.         B9       TXI_DATA_N99       "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode.         A10       TXI_DATA_N9       "I" channel data bit 8.         B10       TXI_DATA_N8       "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode.         B61       GROUND       Digital Ground         B62       GROUND       Digital Ground         B63       GROUND       Digital Ground         B64       GROUND       Digital Ground         B65       GROUND       Digital Ground         B67       GROUND       Digital Ground         B68       GROUND       Digital Ground <td>B4</td> <td>TXI_DATA_N14</td> <td>"I" channel data bit 14, negative side in LVDS mode. Not used in CMOS mode.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | B4   | TXI_DATA_N14 | "I" channel data bit 14, negative side in LVDS mode. Not used in CMOS mode.                 |

| A6 TXI_DATA_P12 "I" channel data bit 12. B6 TXI_DATA_N12 "I" channel data bit 12, negative side in LVDS mode. Not used in CMOS mode. A7 TXI_DATA_P11 "I" channel data bit 11. B7 TXI_DATA_N11 "I" channel data bit 11. B8 TXI_DATA_N10 "I" channel data bit 11, negative side in LVDS mode. Not used in CMOS mode. A8 TXI_DATA_N10 "I" channel data bit 10, negative side in LVDS mode. Not used in CMOS mode. A9 TXI_DATA_N10 "I" channel data bit 9. B9 TXI_DATA_N9 "II" channel data bit 9. B9 TXI_DATA_N9 "II" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode. A10 TXI_DATA_N9 "I" channel data bit 8. B10 TXI_DATA_N9 "I" channel data bit 8. B10 TXI_DATA_N9 "II" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode. B61 GROUND Digital Ground B62 GROUND Digital Ground B63 GROUND Digital Ground B64 GROUND Digital Ground B65 GROUND Digital Ground B66 GROUND Digital Ground B67 GROUND Digital Ground B68 GROUND Digital Ground B69 GROUND Digital Ground B69 GROUND Digital Ground B60 GROUND Digital Ground B61 GROUND Digital Ground B62 GROUND Digital Ground B63 GROUND Digital Ground B64 GROUND Digital Ground B65 GROUND Digital Ground B66 GROUND Digital Ground B67 GROUND Digital Ground B68 GROUND Digital Ground B69 GROUND Digital Ground B60 GROUND Digital Ground B61 GROUND Digital Ground B62 GROUND Digital Ground B63 GROUND Digital Ground B64 GROUND Digital Ground B65 GROUND Digital Ground B66 GROUND Digital Ground B67 GROUND Digital Ground B68 GROUND Digital Ground B69 GROUND Digital Ground B60 GROUND Digital Ground B61 GROUND Digital Ground B62 GROUND Digital Ground B63 GROUND Digital Ground B64 GROUND Digital Ground B65 GROUND Digital Ground                                                                                                                                                                                                                                                                                                                                                                                  | A5   | TXI_DATA_P13 | "I" channel data bit 13.                                                                    |

| B6 TXI_DATA_N12 "I" channel data bit 12, negative side in LVDS mode. Not used in CMOS mode. A7 TXI_DATA_P11 "I" channel data bit 11. B7 TXI_DATA_N11 "I" channel data bit 11. B8 TXI_DATA_N10 "I" channel data bit 10. B8 TXI_DATA_N10 "I" channel data bit 10. B9 TXI_DATA_N10 "I" channel data bit 10. B9 TXI_DATA_N10 "I" channel data bit 19. B9 TXI_DATA_N9 "I" channel data bit 9. B9 TXI_DATA_N9 "I" channel data bit 9. B1 TXI_DATA_N9 "I" channel data bit 8. B10 TXI_DATA_N9 "I" channel data bit 8. B10 TXI_DATA_N9 "I" channel data bit 8. B10 TXI_DATA_N8 "I" channel data bit 18. B10 TXI_DATA_N8 "I" channel data bit 18. B11 TXI_DATA_N8 "I" channel data bit 18. B12 TXI_DATA_N8 "I" channel data bit 15. B13 TXI_DATA_N15 "Q" channel data bit 15. B14 TXI_DATA_N15 "Q" channel data bit 15. B15 TXI_DATA_N15 "Q" channel data bit 15. B16 TXI_DATA_N15 "Q" channel data bit 15. B17 TXI_DATA_N15 "Q" channel data bit 15. B18 TXI_DATA_N15 "Q" channel data bit | B5   | TXI_DATA_N13 | "I" channel data bit 13, negative side in LVDS mode. Not used in CMOS mode.                 |

| A7 TXI_DATA_P11 "I" channel data bit 11. B7 TXI_DATA_N11 "I" channel data bit 11, negative side in LVDS mode. Not used in CMOS mode. A8 TXI_DATA_P10 "I" channel data bit 10. B8 TXI_DATA_N10 "I" channel data bit 10, negative side in LVDS mode. Not used in CMOS mode. A9 TXI_DATA_P9 "I" channel data bit 9. B9 TXI_DATA_N9 "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode. A10 TXI_DATA_P8 "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode. A10 TXI_DATA_N8 "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode. B10 TXI_DATA_N8 "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode. B11 GROUND Digital Ground B12 GROUND Digital Ground B13 GROUND Digital Ground B14 GROUND Digital Ground B15 GROUND Digital Ground B16 GROUND Digital Ground B16 GROUND Digital Ground B17 GROUND Digital Ground B18 GROUND Digital Ground B18 GROUND Digital Ground B19 GROUND Digital Ground B19 GROUND Digital Ground B10 GROUND Digital Ground B10 GROUND Digital Ground B11 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)  D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  D2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  TXQ_DATA_P15 "Q" channel data bit 15.  TXQ_DATA_P15 "Q" channel data bit 15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A6   | TXI_DATA_P12 | "I" channel data bit 12.                                                                    |

| B7TXI_DATA_N11"I" channel data bit 11, negative side in LVDS mode. Not used in CMOS mode.A8TXI_DATA_P10"I" channel data bit 10.B8TXI_DATA_N10"I" channel data bit 10, negative side in LVDS mode. Not used in CMOS mode.A9TXI_DATA_P9"I" channel data bit 9.B9TXI_DATA_N9"I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode.A10TXI_DATA_N8"I" channel data bit 8.B10TXI_DATA_N8"I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode.BG1GROUNDDigital GroundBG2GROUNDDigital GroundBG3GROUNDDigital GroundBG4GROUNDDigital GroundBG5GROUNDDigital GroundBG6GROUNDDigital GroundBG7GROUNDDigital GroundBG8GROUNDDigital GroundBG9GROUNDDigital GroundBG10GROUNDDigital GroundBG2GROUNDDigital GroundBG3GROUNDDigital GroundBG4GROUNDDigital GroundBG5ROUNDDigital GroundBG6ROUNDDigital GroundBG7No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)D1N/CNo Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)D2N/CNo Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)C3TXQ_DATA_N15"Q" channel data bit 15, neg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | В6   | TXI_DATA_N12 | "I" channel data bit 12, negative side in LVDS mode. Not used in CMOS mode.                 |

| A8 TXI_DATA_P10 "I" channel data bit 10. B8 TXI_DATA_N10 "I" channel data bit 10, negative side in LVDS mode. Not used in CMOS mode. A9 TXI_DATA_P9 "I" channel data bit 9. B9 TXI_DATA_P9 "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode. A10 TXI_DATA_P8 "I" channel data bit 8. B10 TXI_DATA_N8 "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode. BG1 GROUND Digital Ground BG2 GROUND Digital Ground BG3 GROUND Digital Ground BG4 GROUND Digital Ground BG5 GROUND Digital Ground BG6 GROUND Digital Ground BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digi | A7   | TXI DATA P11 | "I" channel data bit 11.                                                                    |

| TXI_DATA_N10 "I" channel data bit 10, negative side in LVDS mode. Not used in CMOS mode.  A9 TXI_DATA_P9 "I" channel data bit 9.  B9 TXI_DATA_N9 "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode.  A10 TXI_DATA_P8 "I" channel data bit 8.  B10 TXI_DATA_N8 "I" channel data bit 8.  B10 TXI_DATA_N8 "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode.  BG1 GROUND Digital Ground  BG2 GROUND Digital Ground  BG3 GROUND Digital Ground  BG4 GROUND Digital Ground  BG5 GROUND Digital Ground  BG6 GROUND Digital Ground  BG7 GROUND Digital Ground  BG8 GROUND Digital Ground  BG9 GROUND Digital Ground  BG10 GROUND Digital Ground  C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)  C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  C3 TXQ_DATA_P15 "Q" channel data bit 15.  C4 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | В7   | TXI DATA N11 | "I" channel data bit 11, negative side in LVDS mode. Not used in CMOS mode.                 |

| A9 TXI_DATA_P9 "I" channel data bit 9. B9 TXI_DATA_N9 "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode. A10 TXI_DATA_P8 "I" channel data bit 8. B10 TXI_DATA_N8 "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode. BG1 GROUND Digital Ground BG2 GROUND Digital Ground BG3 GROUND Digital Ground BG4 GROUND Digital Ground BG5 GROUND Digital Ground BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BC9 GROUND Digital Ground BC9 GROUND Digital Ground BC9 GROUND Digital Ground BC9 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3) D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3) D2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3) C3 TXQ_DATA_P15 "Q" channel data bit 15. D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A8   | TXI DATA P10 | "I" channel data bit 10.                                                                    |

| B9 TXI_DATA_N9 "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode. A10 TXI_DATA_P8 "I" channel data bit 8. B10 TXI_DATA_N8 "I" channel data bit 8. B10 TXI_DATA_N8 "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode. BG1 GROUND Digital Ground BG2 GROUND Digital Ground BG3 GROUND Digital Ground BG4 GROUND Digital Ground BG5 GROUND Digital Ground BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)  D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  D2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  C3 TXQ_DATA_P15 "Q" channel data bit 15. C4 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | B8   | TXI DATA N10 | "I" channel data bit 10, negative side in LVDS mode. Not used in CMOS mode.                 |

| A10 TXI_DATA_P8 "I" channel data bit 8. B10 TXI_DATA_N8 "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode. BG1 GROUND Digital Ground BG2 GROUND Digital Ground BG3 GROUND Digital Ground BG4 GROUND Digital Ground BG5 GROUND Digital Ground BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BG10 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)  C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  C3 TXQ_DATA_P15 "Q" channel data bit 15. C4 TXQ_DATA_N15 "Q" channel data bit 15. C6 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A9   | TXI DATA P9  | "I" channel data bit 9.                                                                     |

| B10 TXI_DATA_N8 "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode. BG1 GROUND Digital Ground BG2 GROUND Digital Ground BG3 GROUND Digital Ground BG4 GROUND Digital Ground BG5 GROUND Digital Ground BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)  D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  C3 TXQ_DATA_P15 "Q" channel data bit 15. C3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | В9   | TXI DATA N9  | "I" channel data bit 9, negative side in LVDS mode. Not used in CMOS mode.                  |

| BG1 GROUND Digital Ground BG2 GROUND Digital Ground BG3 GROUND Digital Ground BG4 GROUND Digital Ground BG5 GROUND Digital Ground BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BG10 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)  D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3)  C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  C3 TXQ_DATA_P15 "Q" channel data bit 15.  C6 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A10  | TXI DATA P8  | "I" channel data bit 8.                                                                     |

| BG2 GROUND Digital Ground BG3 GROUND Digital Ground BG4 GROUND Digital Ground BG5 GROUND Digital Ground BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BG10 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3) D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3) C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3) C3 TXQ_DATA_P15 "Q" channel data bit 15. C4 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | B10  | TXI DATA N8  | "I" channel data bit 8, negative side in LVDS mode. Not used in CMOS mode.                  |

| BG3 GROUND Digital Ground BG4 GROUND Digital Ground BG5 GROUND Digital Ground BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BG10 GROUND Digital Ground BG10 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3) D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3) C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3) D2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3) C3 TXQ_DATA_P15 "Q" channel data bit 15. D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BG1  | GROUND       | Digital Ground                                                                              |

| BG3 GROUND Digital Ground BG4 GROUND Digital Ground BG5 GROUND Digital Ground BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BG10 GROUND Digital Ground BG10 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3) D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3) C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3) D2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3) C3 TXQ_DATA_P15 "Q" channel data bit 15. D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BG2  | GROUND       | Digital Ground                                                                              |

| BG5 GROUND Digital Ground BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG9 GROUND Digital Ground BG10 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3) D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3) C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3) C3 TXQ_DATA_P15 "Q" channel data bit 15. C4 DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BG3  | GROUND       | -                                                                                           |

| BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG10 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)  D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3)  C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  TXQ_DATA_P15 "Q" channel data bit 15.  D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BG4  | GROUND       | Digital Ground                                                                              |

| BG6 GROUND Digital Ground BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG10 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3) D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3) C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3) D2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3) C3 TXQ_DATA_P15 "Q" channel data bit 15. D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BG5  | GROUND       |                                                                                             |

| BG7 GROUND Digital Ground BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG10 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3) D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3) C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3) D2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3) C3 TXQ_DATA_P15 "Q" channel data bit 15. D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BG6  | GROUND       | -                                                                                           |

| BG8 GROUND Digital Ground BG9 GROUND Digital Ground BG10 GROUND Digital Ground C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3) D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3) C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3) D2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3) C3 TXQ_DATA_P15 "Q" channel data bit 15. D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BG7  | GROUND       |                                                                                             |

| BG9 GROUND Digital Ground  BG10 GROUND Digital Ground  C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)  D1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3)  C2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  D2 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  C3 TXQ_DATA_P15 "Q" channel data bit 15.  D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BG8  | GROUND       |                                                                                             |

| BG10 GROUND Digital Ground  No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)  N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3)  N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  TXQ_DATA_P15 "Q" channel data bit 15.  TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | GROUND       | 9                                                                                           |

| C1 N/C No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, positive side (DPG3)  No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 1, negative side (DPG3)  No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  TXQ_DATA_P15 "Q" channel data bit 15.  TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | BG10 | GROUND       |                                                                                             |

| Side (DPG3)  No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, positive side (DPG3)  No Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  TXQ_DATA_P15 "Q" channel data bit 15.  TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C1   | N/C          |                                                                                             |

| Side (DPG3)  N/C  N/C  NO Connect (DPG2) / "Q" channel bi-directional, low-speed LVDS 0, negative side (DPG3)  TXQ_DATA_P15 "Q" channel data bit 15.  D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D1   | N/C          |                                                                                             |

| side (DPG3)  C3 TXQ_DATA_P15 "Q" channel data bit 15.  D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C2   | N/C          |                                                                                             |

| D3 TXQ_DATA_N15 "Q" channel data bit 15, negative side in LVDS mode. Not used in CMOS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D2   | N/C          |                                                                                             |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | C3   | TXQ_DATA_P15 | "Q" channel data bit 15.                                                                    |