# **AMMP-6333**

# 18 – 33 GHz, 0.2 W Driver Amplifier in SMT Package

# **Data Sheet**

#### **Description**

The AMMP-6333 is a broadband 0.2 W driver amplifier designed for use in transmitters operating in various frequency bands from 18 GHz to 33 GHz. This small, easy to use device provides over 23 dBm of output power (P-1dB) and more than 20 dB of gain at 25 GHz. It was optimized for linear operation with an output power at the third order intercept point (OIP3) of 30dBm. The AMMP-6333 features a temperature compensated RF power detection circuit that enables power detection sensitivity of 0.3 V/W at 25GHz. It is fabricated using Avago Technologies unique 0.25  $\mu$ m E-mode PHEMT technology which eliminates the need for negative gate biasing voltage.

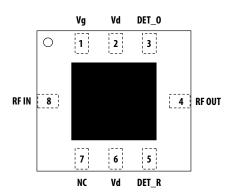

### **Package Diagram**

#### **Features**

• Frequency range: 18 to 33 GHz

• Small signal gain: 20 dB

• P-1dB: 23dBm

• Return Loss (In/Out): -10 dB

#### **Applications**

• Microwave Radio systems

Satellite VSAT, Up/Down Link

• LMDS & Pt-Pt mmW Long Haul

Broadband Wireless Access (including 802.16 and 802.20 WiMax)

• WLL and MMDS loops

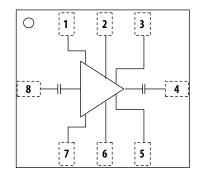

#### **Functional Block Diagram**

| Pin | Function |

|-----|----------|

| 1   | Vg       |

| 2   | Vd       |

| 3   | DET_O    |

| 4   | RF_out   |

| 5   | DET_R    |

| 6   | Vd       |

| 7   | NC       |

| 8   | RF_in    |

Attention: Observe precautions for handling electrostatic sensitive devices.

ESD Machine Model (Class A) = 90 V

ESD Human Body Model (Class 1A) = 300 V

Refer to Avago Application Note A004R:

Electrostatic Discharge, Damage and Control.

Note: MSL Rating = Level 2A

#### **Electrical Specifications**

- 1. Small/Large -signal data measured in a fully de-embedded test fixture form TA = 25°C.

- 2. Pre-assembly into package performance verified 100% on-wafer per AMMC-6220 published specifications.

- 3. This final package part performance is verified by a functional test correlated to actual performance at one or more frequencies.

- 4. Specifications are derived from measurements in a  $50 \Omega$  test environment. Aspects of the amplifier performance may be improved over a more narrow bandwidth by application of additional conjugate, linearity, or low noise ( $\Gamma$ opt) matching.

- 5. All tested parameters guaranteed with measurement accuracy +/- 2dB for P1dB of 17,25 and 32GHz +/- 0.5 for Gain of 17GHz, +/- 1 dB for Gain of 25 and 32GHz

**Table 1. RF Electrical Characteristics**

TA=25°C, Vd=3.0V, Id(Q)=230mA, Zin=Zo=50  $\Omega$

|                                             | •   | 17-20GH | z   |     | 20-30GH | z   | :   | 30-33GHz | 2   |      |         |

|---------------------------------------------|-----|---------|-----|-----|---------|-----|-----|----------|-----|------|---------|

| Parameter                                   | Min | Тур     | Max | Min | Тур     | Max | Min | Тур      | Max | Unit | Comment |

| Small Signal Gain, Gain                     | 14  | 16      |     | 19  | 22      |     | 18  | 20.5     |     | dB   |         |

| Output Power at 1dBGain Compression, P1dB   | 18  | 20.5    |     | 22  | 24.5    |     | 21  | 24       |     | dBm  |         |

| Output Power at 3dBGain Compression, P3dB   |     | 21.5    |     |     | 24.5    |     |     | 23.5     |     | dBm  |         |

| Output Third Order Intercept Point,<br>OIP3 |     | 30      |     |     | 30      |     |     | 30       |     | dBm  |         |

| Reverse Isolation, Iso                      |     | 45      |     |     | 45      |     |     | 45       |     | dB   |         |

| Input Return Loss, Rlin                     |     | 10      |     |     | 10      |     |     | 8        |     | dB   |         |

| Output Return Loss, RLout                   |     | 10      |     |     | 14      |     |     | 10       |     | dB   |         |

#### Table 2. Recommended Operating Range

- 1. Ambient operational temperature  $TA = 25^{\circ}C$  unless otherwise noted.

- 2. Channel-to-backside Thermal Resistance (Tchannel (Tc) =  $34^{\circ}$ C) as measured using infrared microscopy. Thermal Resistance at backside temperature (Tb) =  $25^{\circ}$ C calculated from measured data.

| Description                       | Min. | Typical | Max. | Unit | Comments                                              |

|-----------------------------------|------|---------|------|------|-------------------------------------------------------|

| Drain Supply Current, Id          |      | 230     |      | mA   | Vd=5 V, Vg set for typical IdQ –<br>quiescent current |

| Gate Supply Operating Voltage, Vg |      | 2       |      | V    | IdQ = 230 mA                                          |

| Gate Supply Current, Ig           |      | 7       |      | mA   |                                                       |

**Table 3. Thermal Properties**

| Parameter                                 | Test Conditions                                                       | Value                             |  |

|-------------------------------------------|-----------------------------------------------------------------------|-----------------------------------|--|

| Maximum Power Dissipation                 | Tbaseplate = 85°C                                                     | PD = 2.5W<br>Tchannel = 150°C     |  |

| Thermal Resistance, θjc                   | Vd = 5V<br>Id = 230mA<br>PD = 1.15W<br>Tbaseplate = 85°C              | θjc = 27 °C/W<br>Tchannel = 116°C |  |

| Thermal Resistance, θjc<br>Under RF Drive | Vd = 5V<br>Id = 400mA<br>Pout = 24dBm<br>PD = 2W<br>Tbaseplate = 85°C | θjc = 27 °C/W<br>Tchannel = 139°C |  |

# **Absolute Minimum and Maximum Ratings**

# **Table 4. Minimum and Maximum Ratings**

| Description                        | Min. | Max.     | Unit | Comments          |

|------------------------------------|------|----------|------|-------------------|

| Drain to Gate Voltage, Vd-Vg       |      | 14       | V    |                   |

| Positive Supply Voltage, Vd        |      | 5.5      | V    |                   |

| Gate Supply Voltage, Vg            |      | 0 to 2.5 | V    |                   |

| Power Dissipation, PD              |      | 2.5      | W    |                   |

| CW Input Power, Pin                |      | 20       | dBm  |                   |

| Channel Temperature, Tch           |      | +150     | °C   |                   |

| Storage Temperature, Tstg          | -65  | +155     | °C   |                   |

| Maximum Assembly Temperature, Tmax |      | 320      | °C   | 30 second maximum |

#### Notes:

<sup>1.</sup> Operation in excess of any one of these conditions may result in permanent damage to this device.

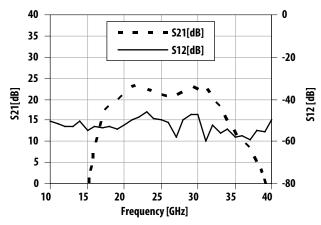

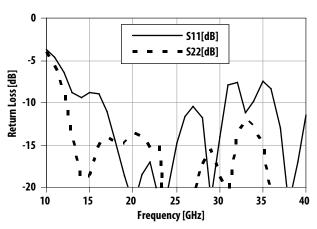

# **Typical Performance**

$$(T_A = 25$$

°C,  $V_d = 5$  V,  $I_{dQ} = 230$  mA,  $Z_{in} = Z_{out} = 50$   $\Omega)$

(Data obtained from a test fixture with 2.4 mm connectors. Effects of the test fixture – losses and mismatch – have not been removed from the data)

Figure 1. Gain and Reverse Isolation vs Frequency

Figure 2. Return Loss vs Frequency

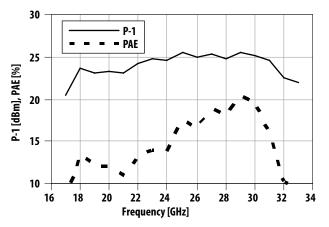

Figure 3. P-1dB and PAE vs Frequency

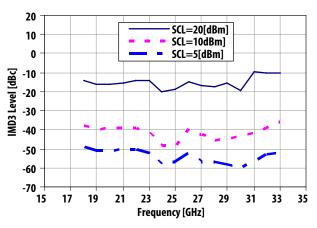

Figure 4. Typical IMD3 vs Frequency (SCL = Single Carrier level)

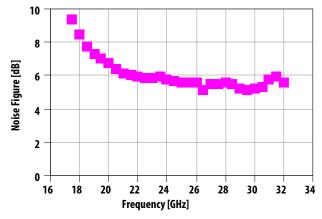

Figure 5. Typical Noise Figure vs Frequency

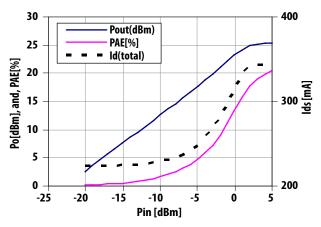

Figure 6. Output Power, PAE, and Drain Current vs Input Power at 30GHz

# **Typical Performance** (continued)

$$(T_A = 25$$

°C,  $Z_{in} = Z_{out} = 50 \Omega)$

(Data obtained from a test fixture with 2.4 mm connectors. Effects of the test fixture – losses and mismatch – have not been removed from the data)

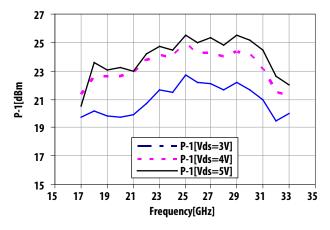

Figure 7.  $P_{-1dB}$  vs Frequency and Vds, ( $I_{dQ}$ =230mA)

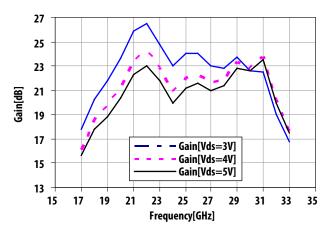

Figure 8. Small signal gain vs Frequency and I<sub>dQ</sub>, (Vds=5V)

Figure 9. Small signal gain vs Frequency and Vds, (IdQ=230mA)

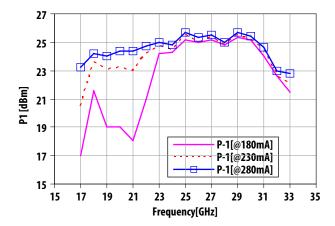

Figure 10. P<sub>-1dB</sub> vs Frequency and I<sub>dQ</sub>, (Vds=5V)

# **Typical Performance** (continued)

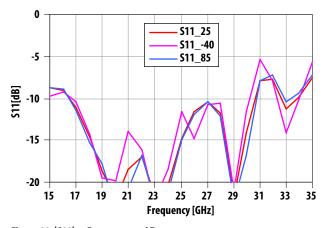

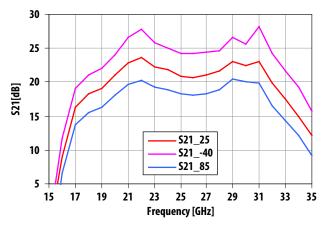

$$(V_d = 5 \text{ V}, I_{dQ} = 230 \text{ mA}, Z_{in} = Z_{out} = 50 \Omega)$$

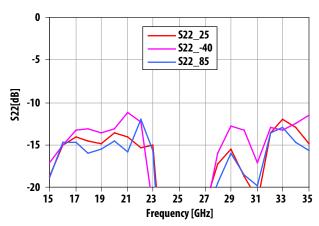

(Data obtained from a test fixture with 2.4 mm connectors. Effects of the test fixture – losses and mismatch – have not been removed from the data)

Figure 11. |S11| vs Frequency and Temperature

Figure 12. |S22| vs Frequency and Temperature

Figure 13. |S21| vs Frequency and Temperature

Figure 14. P<sub>-1dB</sub> vs Frequency and Temperature

#### **Biasing Considerations**

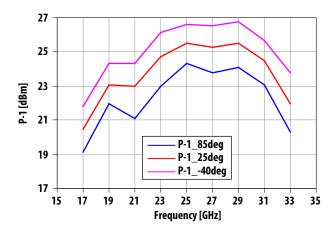

The AMMP-6333 is a balanced amplifier consisting of two four stage single-ended amplifiers, two Lange couplers, a power monitoring detector, a reference detector for temperature compensation, and a current mirror for the gate biasing (Figure 15).

The recommended quiescent DC bias conditions for optimum gain, output power, efficiency, and reliability are: Vd = 5 V with Vg set for  $I_{dQ} = 230$  mA. The drain bias voltage range is from 3 to 5 V. Drain current range is from 200 mA to 350 mA. The AMMC-6333 can be biased with a dual or single positive DC source (Figure 16).

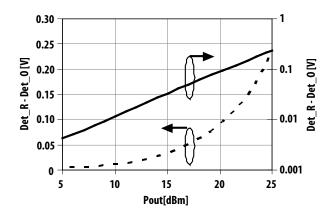

The output power detection network provides a way to monitor output power. The differential voltage between the DET\_R and DET\_O outputs can be correlated with the RF power emerging from the RF output port. This voltage is given by:

$$V = (V_{DET\_R} - V_{DET\_O}) - V_{OFS}$$

Where:

$V_{DET\_R}$  is the voltage at the DET\_R port  $V_{DET\_O}$  is a voltage at the DET\_O port  $V_{OFS}$  is the offset voltage at zero input power

The offset voltage (V<sub>OFS</sub>) can be at each power level by turning off the input power and measuring V. The error due to temperature drift should be less than 0.01dB/50°C. When V<sub>OFS</sub> is determined at a single reference temperature the drift error should be less than 0.25dB. Finally, V<sub>OFS</sub> be characterized over a range of temperatures and stored in a lookup table, or it can be measured at two temperatures and a linear fit used to calculate V<sub>OFS</sub> at any temperature.

The RF ports are AC coupled at the RF input to the first stage and the RF output of the final stage. No ground wires are needed since ground connections are made with plated through-holes to the backside of the device.

Figure 15. AMMC-6333 schematic

# 1. Dual positive DC power supply

#### 100 pF 1 F 100 p 100 pF **1**μ**F** 400 DET\_0 ♠ DET\_0 1 0 0 2 RF Input RF Output **RF Input RF Output** 8 8 7 6 5 6 5 DET\_R DET\_R 100 pF 100 pF 1. Vdd may be applied to either Pin 2 or Pin 6.

2. Single positive DC power supply

Figure 16. AMMP-6333 assembly examples, Vd pins must be biased from both sides

Figure 17. AMMP-6333 Typical Detector Voltage and Output Power, Freq=30GHz

# **Typical Scattering Parameters**

Please refer to <a href="http://www.avagotech.com">http://www.avagotech.com</a> for typical scattering parameters data.

# Package Dimension, PCB Layout and Tape and Reel information

Please refer to Avago Technologies Application Note 5520, AMxP-xxxx production Assembly Process (Land Pattern A).

# **Ordering Information**

|                | Devices Per |                |

|----------------|-------------|----------------|

| Part Number    | Container   | Container      |

| AMMP-6333-BLKG | 10          | Antistatic bag |

| AMMP-6333-TR1G | 100         | 7" Reel        |

| AMMP-6333-TR2G | 500         | 7" Reel        |

For product information and a complete list of distributors, please go to our web site: **www.avagotech.com**